# LPC3141/3143

Low-cost, low-power ARM926EJ microcontrollers with USB High-speed OTG, SD/MMC, and NAND flash controller

Rev. 1 — 4 June 2012

**Product data sheet**

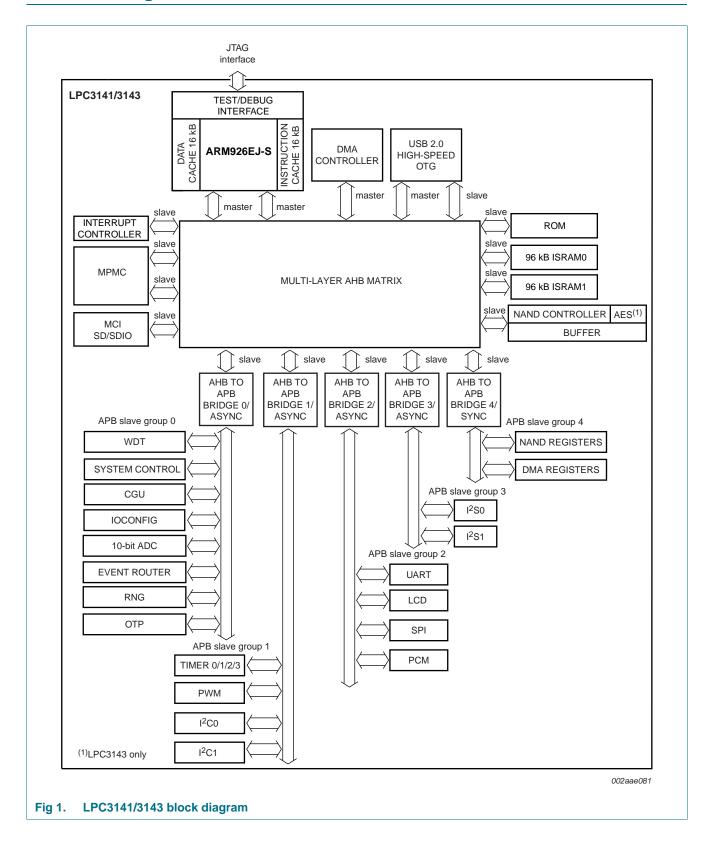

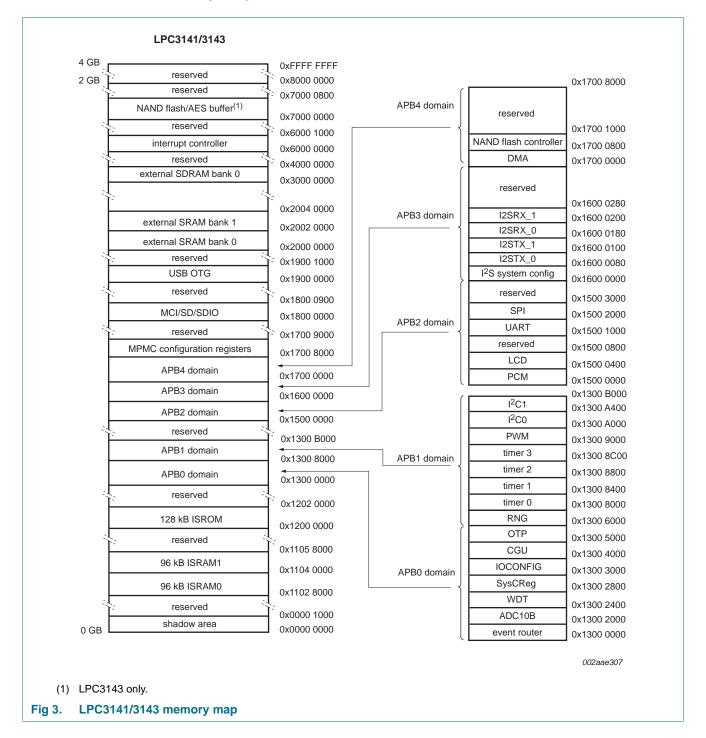

## 1. General description

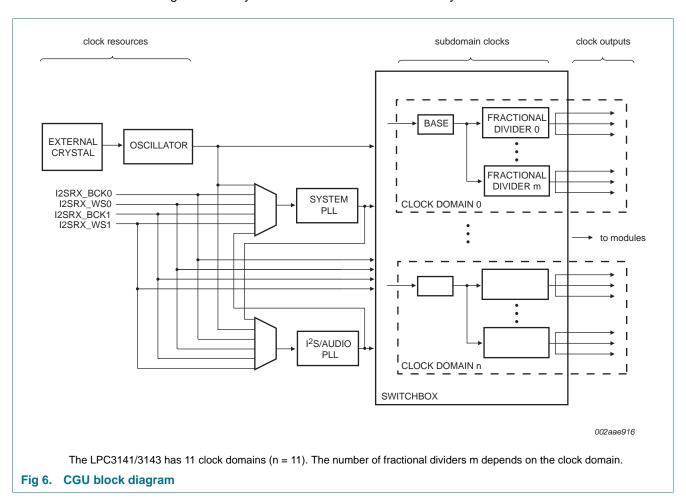

The NXP LPC3141/3143 combine a 270 MHz ARM926EJ-S CPU core, High-speed USB 2.0 OTG, 192 KB SRAM, NAND flash controller, flexible external bus interface, four channel 10-bit A/D, and a myriad of serial and parallel interfaces in a single chip targeted at consumer, industrial, medical, and communication markets. To optimize system power consumption, the LPC3141/3143 have multiple power domains and a very flexible Clock Generation Unit (CGU) that provides dynamic clock gating and scaling.

## 2. Features and benefits

## 2.1 Key features

- CPU platform

- ◆ 270 MHz, 32-bit ARM926EJ-S

- ◆ 16 kB D-cache and 16 kB I-cache

- Memory Management Unit (MMU)

- Internal memory

- ◆ 192 kB embedded SRAM

- External memory interface

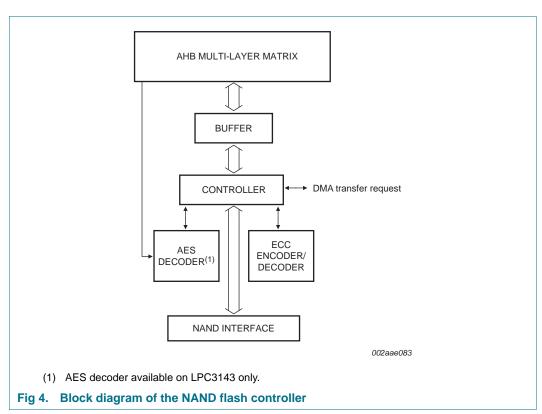

- ◆ NAND flash controller with 8-bit ECC and AES decryption support (LPC3143 only)

- ◆ 8/16-bit Multi-Port Memory Controller (MPMC): SDRAM and SRAM

- Security

- ◆ AES decryption engine (LPC3143 only)

- Secure one-time programmable memory for AES key storage and customer use

- ◆ 128 bit unique ID per device for DRM schemes

- Communication and connectivity

- ◆ High-speed USB 2.0 (OTG, Host, Device) with on-chip PHY

- ◆ Two I<sup>2</sup>S interfaces

- Integrated master/slave SPI

- ◆ Two master/slave I<sup>2</sup>C-bus interfaces

- Fast UART

- Memory Card Interface (MCI): MMC/SD/SDIO/CE-ATA

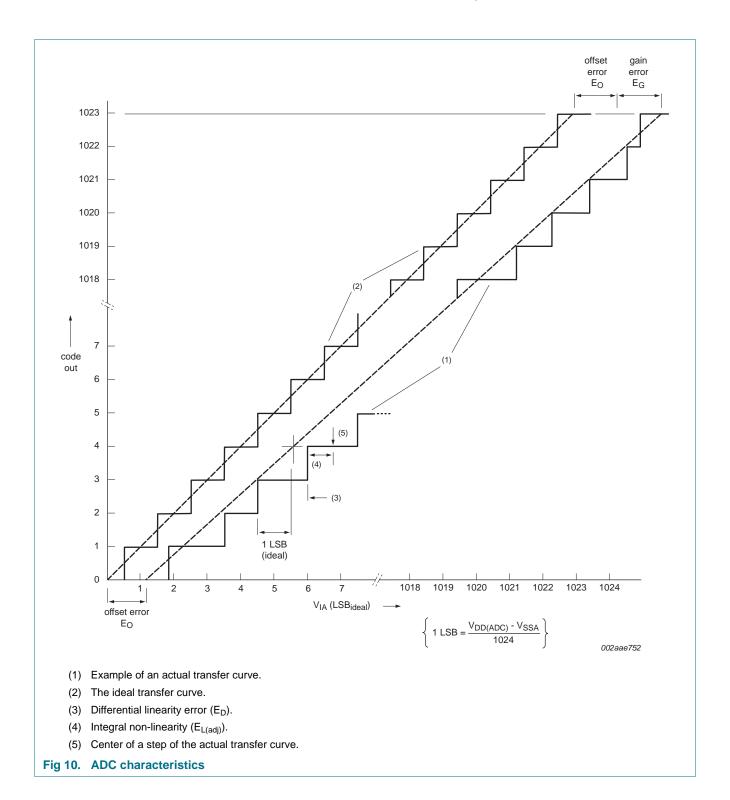

- ◆ Four-channel 10-bit ADC

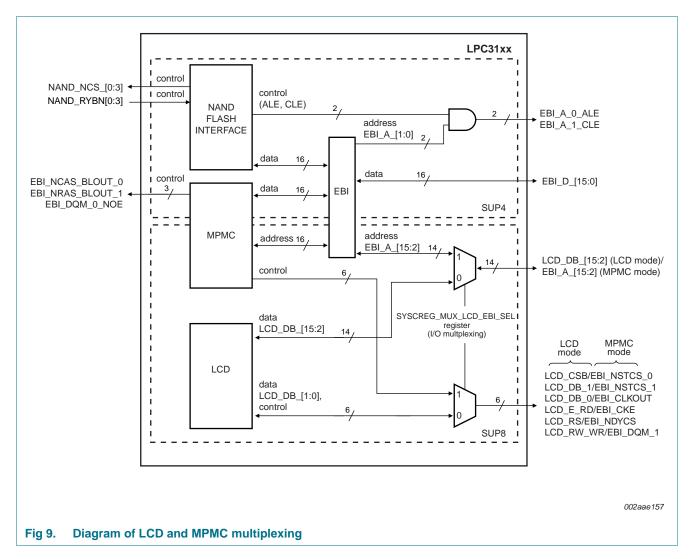

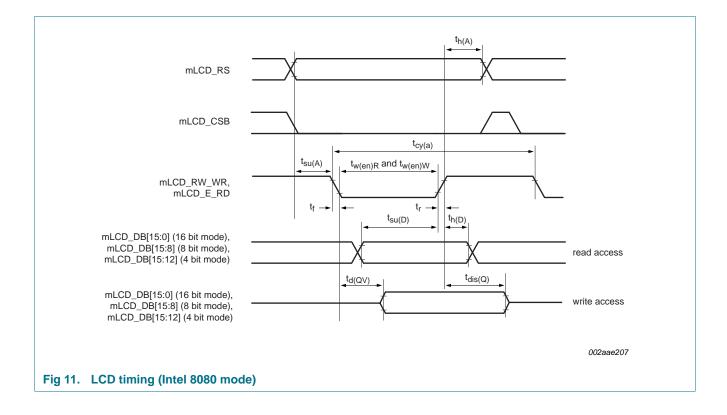

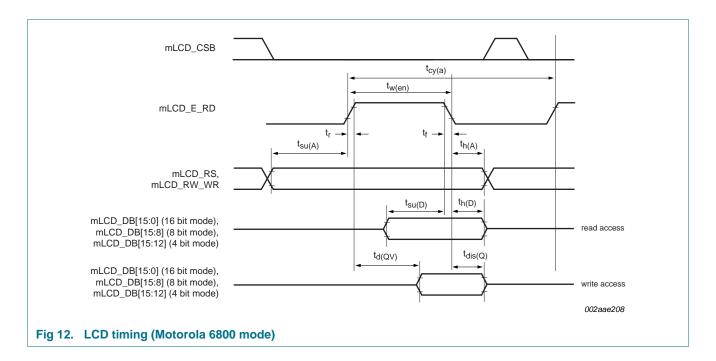

- Integrated 4/8/16-bit 6800/8080 compatible LCD interface

- System functions

- Dynamic clock gating and scaling

- Multiple power domains

- Selectable boot-up: SPI flash, NAND flash, SD/MMC cards, UART, or USB

- On the LPC3143 only: secure booting using an AES decryption engine from SPI flash, NAND flash, SD/MMC cards, UART, or USB.

- DMA controller

- ◆ Four 32-bit timers

- Watchdog timer

- PWM module

- ◆ Master/slave PCM interface

- Random Number Generator (RNG)

- ◆ General Purpose I/O pins (GPIO)

- Flexible and versatile interrupt structure

- ◆ JTAG interface with boundary scan and ARM debug access

- Operating voltage and temperature

- Core voltage: 1.2 V

- ◆ I/O voltages: 1.8 V, 3.3 V

- ◆ Temperature: –40 °C to +85 °C

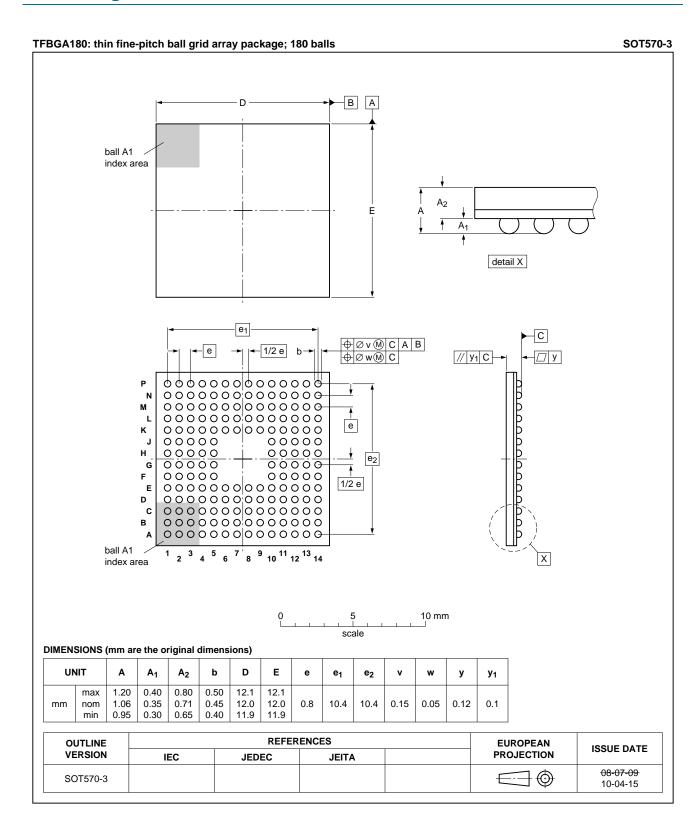

- TFBGA180 package: 12 x 12 mm, 0.8 mm pitch

# 3. Ordering information

#### Table 1. Ordering information

| Type number   | Package  |                                                                                                 |          |

|---------------|----------|-------------------------------------------------------------------------------------------------|----------|

|               | Name     | Description                                                                                     | Version  |

| LPC3141FET180 | TFBGA180 | Plastic thin fine pitch ball grid array package, 180 balls, body 12 $\times$ 12 $\times$ 0.8 mm | SOT570-3 |

| LPC3143FET180 | TFBGA180 | Plastic thin fine pitch ball grid array package, 180 balls, body 12 $\times$ 12 $\times$ 0.8 mm | SOT570-3 |

## 3.1 Ordering options

Table 2. Ordering options for LPC3141/3143

| Type number   | Core/bus<br>frequency | Total<br>SRAM | Security<br>engine<br>AES | High-speed USB      | 10-bit<br>ADC<br>channels | I <sup>2</sup> S/<br>I <sup>2</sup> C | MCI<br>SDHC/<br>SDIO/<br>CE-ATA | Temperature range |

|---------------|-----------------------|---------------|---------------------------|---------------------|---------------------------|---------------------------------------|---------------------------------|-------------------|

| LPC3141FET180 | 270/<br>90 MHz        | 192 kB        | no                        | Device/<br>Host/OTG | 4                         | 2 each                                | yes                             | –40 °C to +85 °C  |

| LPC3143FET180 | 270/<br>90 MHz        | 192 kB        | yes                       | Device/<br>Host/OTG | 4                         | 2 each                                | yes                             | –40 °C to +85 °C  |

# 4. Block diagram

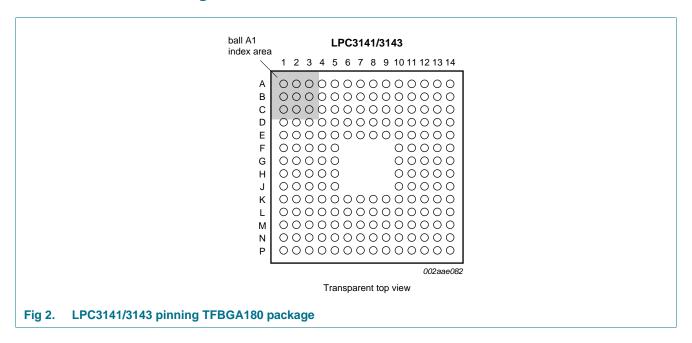

# 5. Pinning information

## 5.1 Pinning

Table 3. Pin allocation table

| Pin | Symbol        | Pin | Symbol      | Pin | Symbol      | Pin | Symbol      |  |  |

|-----|---------------|-----|-------------|-----|-------------|-----|-------------|--|--|

| Rov | v A           |     |             |     |             | •   |             |  |  |

| 1   | EBI_D_10      | 2   | EBI_A_1_CLE | 3   | EBI_D_9     | 4   | mGPIO10     |  |  |

| 5   | mGPIO7        | 6   | mGPIO6      | 7   | SPI_CS_OUT0 | 8   | SPI_SCK     |  |  |

| 9   | VPP           | 10  | FFAST_IN    | 11  | VSSI        | 12  | ADC10B_GNDA |  |  |

| 13  | ADC10B_VDDA33 | 14  | ADC10B_GPA1 | -   | -           | -   | -           |  |  |

| Rov | Row B         |     |             |     |             |     |             |  |  |

| 1   | EBI_D_8       | 2   | VDDE_IOA    | 3   | EBI_A_0_ALE | 4   | mNAND_RYBN2 |  |  |

| 5   | mGPIO8        | 6   | mGPIO5      | 7   | SPI_MOSI    | 8   | SPI_CS_IN   |  |  |

| 9   | PWM_DATA      | 10  | FFAST_OUT   | 11  | GPIO3       | 12  | VSSE_IOC    |  |  |

| 13  | ADC10B_GPA2   | 14  | ADC10B_GPA0 | -   | -           | -   | -           |  |  |

| Rov | v C           |     |             |     |             |     |             |  |  |

| 1   | EBI_D_7       | 2   | EBI_D_11    | 3   | VSSE_IOA    | 4   | VSSE_IOA    |  |  |

| 5   | mGPIO9        | 6   | VDDI        | 7   | VSSI        | 8   | SPI_MISO    |  |  |

| 9   | VPP           | 10  | I2C_SDA0    | 11  | GPIO4       | 12  | VDDI        |  |  |

| 13  | VDDE_IOC      | 14  | ADC10B_GPA3 | -   | -           | -   | -           |  |  |

| Rov | v D           |     |             |     |             |     |             |  |  |

| 1   | EBI_D_5       | 2   | EBI_D_6     | 3   | EBI_D_13    | 4   | mNAND_RYBN3 |  |  |

| 5   | VDDE_IOC      | 6   | VSSE_IOC    | 7   | VDDE_IOC    | 8   | VSSE_IOC    |  |  |

| 9   | VSSE_IOC      | 10  | I2C_SCL0    | 11  | VDDA12      | 12  | VSSI        |  |  |

| 13  | BUF_TCK       | 14  | BUF_TMS     | -   | -           | -   | -           |  |  |

Table 3.

Pin allocation table ...continued

| Pin | Symbol           | Pin | Symbol           | Pin | Symbol        | Pin | Symbol       |

|-----|------------------|-----|------------------|-----|---------------|-----|--------------|

| Row | <i>I</i> E       |     |                  |     |               |     |              |

| 1   | EBI_D_3          | 2   | EBI_D_4          | 3   | EBI_D_14      | 4   | VSSE_IOA     |

| 5   | VDDE_IOA         | 6   | mNAND_RYBN0      | 7   | mNAND_RYBN1   | 8   | VDDE_IOC     |

| 9   | VSSA12           | 10  | VDDA12           | 11  | ARM_TDO       | 12  | I2C_SDA1     |

| 13  | I2C_SCL1         | 14  | I2STX_BCK1       | -   | -             | -   | -            |

| Row | <i>I</i> F       |     |                  |     |               | '   |              |

| 1   | EBI_D_2          | 2   | EBI_D_1          | 3   | EBI_D_15      | 4   | VSSE_IOA     |

| 5   | VDDE_IOA         | 10  | SCAN_TDO         | 11  | BUF_TRST_N    | 12  | I2STX_DATA1  |

| 13  | I2SRX_WS1        | 14  | I2SRX_BCK1       | -   | -             | -   | -            |

| Row | / G              |     |                  |     |               | '   |              |

| 1   | EBI_NCAS_BLOUT_0 | 2   | EBI_D_0          | 3   | EBI_D_12      | 4   | VSSI         |

| 5   | VDDE_IOA         | 10  | I2STX_WS1        | 11  | VSSE_IOC      | 12  | VDDE_IOC     |

| 13  | SYSCLK_O         | 14  | I2SRX_DATA1      | -   | -             | -   | -            |

| Row | / H              |     |                  |     |               |     |              |

| 1   | EBI_DQM_0_NOE    | 2   | EBI_NRAS_BLOUT_1 | 3   | VDDI          | 4   | VSSE_IOA     |

| 5   | VDDE_IOA         | 10  | GPIO12           | 11  | GPIO19        | 12  | CLK_256FS_O  |

| 13  | GPIO11           | 14  | RSTIN_N          | -   | -             | -   | -            |

| Row | / J              | 1   |                  |     |               |     |              |

| 1   | NAND_NCS_0       | 2   | EBI_NWE          | 3   | NAND_NCS_1    | 4   | CLOCK_OUT    |

| 5   | USB_RREF         | 10  | GPIO1            | 11  | GPIO16        | 12  | GPIO13       |

| 13  | GPIO15           | 14  | GPIO14           | -   | -             | -   | -            |

| Row | <i>i</i> K       |     |                  |     |               |     |              |

| 1   | NAND_NCS_2       | 2   | NAND_NCS_3       | 3   | VSSE_IOA      | 4   | USB_VSSA_REF |

| 5   | mLCD_DB_12       | 6   | mLCD_DB_6        | 7   | mLCD_DB_10    | 8   | mLCD_CSB     |

| 9   | TDI              | 10  | GPIO0            | 11  | VDDE_IOC      | 12  | GPIO17       |

| 13  | GPIO20           | 14  | GPIO18           | -   | -             | -   | -            |

| Row | <i>I</i> L       |     |                  |     |               |     |              |

| 1   | USB_VDDA12_PLL   | 2   | USB_VBUS         | 3   | USB_VSSA_TERM | 4   | VDDE_IOB     |

| 5   | mLCD_DB_9        | 6   | VSSI             | 7   | VDDI          | 8   | mLCD_E_RD    |

| 9   | VSSE_IOC         | 10  | VDDE_IOC         | 11  | VSSI          | 12  | VDDI         |

| 13  | VSSE_IOC         | 14  | GPIO2            | -   | -             | -   | -            |

| Row | / M              |     |                  |     |               |     |              |

| 1   | USB_ID           | 2   | USB_VDDA33_DRV   | 3   | VSSE_IOB      | 4   | VSSE_IOB     |

| 5   | VDDE_IOB         | 6   | VSSE_IOB         | 7   | VDDE_IOB      | 8   | VSSE_IOB     |

| 9   | VDDE_IOB         | 10  | I2SRX_DATA0      | 11  | mI2STX_WS0    | 12  | ml2STX_BCK0  |

| 13  | mI2STX_DATA0     | 14  | TCK              | -   | -             | -   | -            |

| Row | / N              | 1   |                  | 1   |               | 1   |              |

| 1   | USB_GNDA         | 2   | USB_DM           | 3   | mLCD_DB_15    | 4   | mLCD_DB_11   |

| 5   | mLCD_DB_8        | 6   | mLCD_DB_2        | 7   | mLCD_DB_4     | 8   | mLCD_DB_0    |

| 9   | mLCD_RW_WR       | 10  | I2SRX_BCK0       | 11  | JTAGSEL       | 12  | UART_TXD     |

| 13  | mUART_CTS_N      | 14  | ml2STX_CLK0      |     | -             | _   | <del>_</del> |

Table 3.

Pin allocation table ...continued

| Pin | Symbol     | Pin | Symbol      | Pin | Symbol     | Pin | Symbol     |

|-----|------------|-----|-------------|-----|------------|-----|------------|

| Rov | w P        |     |             |     |            |     |            |

| 1   | USB_VDDA33 | 2   | USB_DP      | 3   | mLCD_DB_14 | 4   | mLCD_DB_13 |

| 5   | mLCD_DB_7  | 6   | mLCD_DB_3   | 7   | mLCD_DB_5  | 8   | mLCD_RS    |

| 9   | mLCD_DB_1  | 10  | TMS         | 11  | I2SRX_WS0  | 12  | UART_RXD   |

| 13  | TRST_N     | 14  | mUART_RTS_N | -   | -          | -   | -          |

## Table 4. Pin description

Pin names with prefix m are multiplexed pins. See Table 10 for pin function selection of multiplexed pins.

| Pin name                | BGA<br>Ball | Digital<br>I/O<br>level | Application function | Pin<br>state<br>after<br>reset <sup>[2]</sup> | Cell type [3] | Description                                                                                                                             |

|-------------------------|-------------|-------------------------|----------------------|-----------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Clock Generation Unit ( | CGU)        |                         |                      |                                               |               |                                                                                                                                         |

| FFAST_IN                | A10         | SUP1                    | Al                   | -                                             | AIO2          | 12 MHz oscillator clock input.                                                                                                          |

| FFAST_OUT               | B10         | SUP1                    | AO                   | -                                             | AIO2          | 12 MHz oscillator clock output.                                                                                                         |

| VDDA12                  | D11;<br>E10 | SUP1                    | Supply               | -                                             | PS3           | 12 MHz oscillator/PLLs analog supply.                                                                                                   |

| VSSA12                  | E9          | -                       | Ground               | -                                             | CG1           | 12 MHz oscillator/PLLs analog ground.                                                                                                   |

| RSTIN_N                 | H14         | SUP3                    | DI                   | I:PU                                          | DIO2          | System Reset Input (active LOW).                                                                                                        |

| CLK_256FS_O             | H12         | SUP3                    | DO                   | 0                                             | DIO1          | Programmable clock output; fractionally derived from CLK1024FS_BASE clock domain. Generally used for external audio codec master clock. |

| CLOCK_OUT               | J4          | SUP4                    | DO                   | 0                                             | DIO4          | Programmable clock output; fractionally derived from SYS_BASE clock domain.                                                             |

| SYSCLK_O[4]             | G13         | SUP3                    | DO                   | 0                                             | DIO1          | Programmable clock output. Output one of seven base/reference input clocks. No fractional divider.                                      |

| 10-bit ADC              |             |                         |                      |                                               |               |                                                                                                                                         |

| ADC10B_VDDA33           | A13         | SUP3                    | Supply               | -                                             | PS3           | 10-bit ADC analog supply.                                                                                                               |

| ADC10B_GNDA             | A12         | -                       | Ground               | -                                             | CG1           | 10-bit ADC analog ground.                                                                                                               |

| ADC10B_GPA0             | B14         | SUP3                    | Al                   | -                                             | AIO1          | 10-bit ADC analog input.                                                                                                                |

| ADC10B_GPA1             | A14         | SUP3                    | Al                   | -                                             | AIO1          | 10-bit ADC analog input.                                                                                                                |

| ADC10B_GPA2             | B13         | SUP3                    | Al                   | -                                             | AIO1          | 10-bit ADC analog input.                                                                                                                |

| ADC10B_GPA3             | C14         | SUP3                    | Al                   | -                                             | AIO1          | 10-bit ADC analog input.                                                                                                                |

| USB HS 2.0 OTG          |             |                         |                      |                                               |               |                                                                                                                                         |

| USB_VBUS                | L2          | SUP5                    | Al                   | -                                             | AIO3          | USB supply detection line.                                                                                                              |

| USB_ID                  | M1          | SUP3                    | Al                   | -                                             | AIO1          | Indicates to the USB transceiver whether in device (USB_ID HIGH) or host (USB_ID LOW) mode (contains internal pull-up resistor).        |

| USB_RREF                | J5          | SUP3                    | AIO                  | -                                             | AIO1          | USB connection for external reference resistor (12 k $\Omega$ ± 1%) to analog ground supply.                                            |

| USB_DP                  | P2          | SUP3                    | AIO                  | -                                             | AIO1          | USB D+ connection with integrated 45 $\Omega$ termination resistor.                                                                     |

**Table 4. Pin description** ...continued

Pin names with prefix m are multiplexed pins. See <u>Table 10</u> for pin function selection of multiplexed pins.

| Pin name                              | BGA<br>Ball | Digital<br>I/O<br>level | Application function | Pin<br>state<br>after<br>reset <sup>[2]</sup> | Cell type [3] | Description                                                                                                  |

|---------------------------------------|-------------|-------------------------|----------------------|-----------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------|

| USB_DM                                | N2          | SUP3                    | AIO                  | -                                             | AIO1          | USB D– connection with integrated 45 $\Omega$ termination resistor.                                          |

| USB_VDDA12_PLL                        | L1          | SUP1                    | Supply               | -                                             | PS3           | USB PLL supply.                                                                                              |

| USB_VDDA33_DRV                        | M2          | SUP3                    | Supply               | -                                             | PS3           | USB analog supply for driver.                                                                                |

| USB_VDDA33                            | P1          | SUP3                    | Supply               | -                                             | PS3           | USB analog supply for PHY.                                                                                   |

| USB_VSSA_TERM                         | L3          | -                       | Ground               | -                                             | CG1           | USB analog ground for clean reference for on chip termination resistors.                                     |

| USB_GNDA                              | N1          | -                       | Ground               | -                                             | CG1           | USB analog ground.                                                                                           |

| USB_VSSA_REF                          | K4          | -                       | Ground               | -                                             | CG1           | USB analog ground for clean reference.                                                                       |

| JTAG                                  |             |                         |                      |                                               |               |                                                                                                              |

| JTAGSEL                               | N11         | SUP3                    | DI                   | I:PD                                          | DIO1          | JTAG selection. Controls output function of SCAN_TDO and ARM_TDO signals. Must be LOW during power-on reset. |

| TDI                                   | K9          | SUP3                    | DI                   | I:PU                                          | DIO1          | JTAG data input.                                                                                             |

| TRST_N                                | P13         | SUP3                    | DI                   | I:PD                                          | DIO1          | JTAG TAP Controller Reset Input. Must be LOW during power-on reset.                                          |

| TCK                                   | M14         | SUP3                    | DI                   | I:PD                                          | DIO1          | JTAG clock input.                                                                                            |

| TMS                                   | P10         | SUP3                    | DI                   | I:PU                                          | DIO1          | JTAG mode select input.                                                                                      |

| SCAN_TDO                              | F10         | SUP3                    | DO                   | O/Z                                           | DIO1          | JTAG TDO signal from scan TAP controller.<br>Pin state is controlled by JTAGSEL.                             |

| ARM_TDO                               | E11         | SUP3                    | DO                   | 0                                             | DIO1          | JTAG TPO signal from ARM926 TAP controller.                                                                  |

| BUF_TRST_N                            | F11         | SUP3                    | DO                   | 0                                             | DIO1          | Buffered TRST_N out signal. Used for connecting an on board TAP controller (FPGA, DSP, etc.).                |

| BUF_TCK                               | D13         | SUP3                    | DO                   | 0                                             | DIO1          | Buffered TCK out signal. Used for connecting an on board TAP controller (FPGA, DSP, etc.).                   |

| BUF_TMS                               | D14         | SUP3                    | DO                   | 0                                             | DIO1          | Buffered TMS out signal. Used for connecting an on board TAP controller (FPGA, DSP, etc.).                   |

| UART                                  |             |                         |                      |                                               |               |                                                                                                              |

| mUART_CTS_N[4][5]                     | N13         | SUP3                    | DI/GPIO              | ļ                                             | DIO1          | UART clear to send (active LOW).                                                                             |

| mUART_RTS_N[4][5]                     | P14         | SUP3                    | DO/GPIO              | 0                                             | DIO1          | UART ready to send (active LOW).                                                                             |

| UART_RXD[4]                           | P12         | SUP3                    | DI/GPIO              | I                                             | DIO1          | UART serial input.                                                                                           |

| UART_TXD[4]                           | N12         | SUP3                    | DO/GPIO              | 0                                             | DIO1          | UART serial output.                                                                                          |

| I <sup>2</sup> C-bus master/slave int | terface     |                         |                      |                                               |               |                                                                                                              |

| I2C_SDA0                              | C10         | SUP3                    | DIO                  | ļ                                             | IICD          | I <sup>2</sup> C0-bus serial data line.                                                                      |

| I2C_SCL0                              | D10         | SUP3                    | DIO                  | ļ                                             | IICC          | I <sup>2</sup> C0-bus serial clock line.                                                                     |

| I2C_SDA1[4]                           | E12         | SUP3                    | DIO                  | 0                                             | DIO1          | l <sup>2</sup> C1-bus serial data line.                                                                      |

| I2C_SCL1[4]                           | E13         | SUP3                    | DIO                  | 0                                             | DIO1          | l <sup>2</sup> C1-bus serial clock line.                                                                     |

Table 4. Pin description ...continued

Pin names with prefix m are multiplexed pins. See <u>Table 10</u> for pin function selection of multiplexed pins.

| Pin name                  | BGA<br>Ball                                      |      | Application function |   |      | Description                                    |

|---------------------------|--------------------------------------------------|------|----------------------|---|------|------------------------------------------------|

| Serial Peripheral Interfa | ice (SP                                          | I)   |                      |   |      |                                                |

| SPI_CS_OUT0[4]            | A7                                               | SUP3 | DO                   | 0 | DIO4 | SPI chip select output (master).               |

| SPI_SCK[4]                | A8                                               | SUP3 | DIO                  | I | DIO4 | SPI clock input (slave)/clock output (master). |

| SPI_MISO[4]               | C8                                               | SUP3 | DIO                  | I | DIO4 | SPI data input (master)/data output (slave).   |

| SPI_MOSI4                 | B7                                               | SUP3 | DIO                  | I | DIO4 | SPI data output (master)/data input (slave).   |

| SPI_CS_IN[4]              | B8                                               | SUP3 | DI                   | I | DIO4 | SPI chip select input (slave).                 |

| Digital power supply      |                                                  |      |                      |   |      |                                                |

| VDDI                      | H3;<br>L7;<br>L12;<br>C12;<br>C6                 | SUP1 | Supply               | - | CS2  | Digital core supply.                           |

| VSSI                      | A11;<br>C7;<br>D12;<br>G4;<br>L6;<br>L11         |      | Ground               | - | CG2  | Digital core ground.                           |

| Peripheral power suppl    | у                                                |      |                      |   |      |                                                |

| VDDE_IOA                  | B2;<br>E5;<br>F5;<br>G5;<br>H5                   | SUP4 | Supply               | - | PS1  | Peripheral supply for NAND flash interface.    |

| VDDE_IOB                  | L4;<br>M5;<br>M7;<br>M9                          | SUP8 | Supply               | - | PS1  | Peripheral supply for SDRAM/LCD.               |

| VDDE_IOC                  | C13;<br>D5;<br>D7;<br>E8;<br>G12;<br>L10;<br>K11 | SUP3 | Supply               | - | PS1  | Peripheral supply.                             |

| VSSE_IOA                  | C3;<br>C4;<br>E4;<br>F4;<br>H4;<br>K3            | -    | Ground               | - | PG1  | -                                              |

| VSSE_IOB                  | M3;<br>M4;<br>M6;<br>M8                          | -    | Ground               | - | PG1  | -                                              |

**Table 4. Pin description** ...continued

Pin names with prefix m are multiplexed pins. See Table 10 for pin function selection of multiplexed pins.

| Pin name                             | BGA<br>Ball                                     | Digital<br>I/O<br>level | Application function | Pin<br>state<br>after<br>reset[2] | Cell type [3] | Description                                                    |

|--------------------------------------|-------------------------------------------------|-------------------------|----------------------|-----------------------------------|---------------|----------------------------------------------------------------|

| VSSE_IOC                             | B12;<br>D6;<br>D8;<br>D9;<br>G11;<br>L9;<br>L13 | -                       | Ground               | -                                 | PG1           | -                                                              |

| LCD interface                        |                                                 |                         |                      |                                   |               |                                                                |

| mLCD_CSB[4]                          | K8                                              | SUP8                    | DO                   | 0                                 | DIO4          | LCD chip select (active LOW).                                  |

| mLCD_E_RD[4]                         | L8                                              | SUP8                    | DO                   | 0                                 | DIO4          | LCD 6800 enable or 8080 read enable (active HIGH).             |

| mLCD_RS[4]                           | P8                                              | SUP8                    | DO                   | 0                                 | DIO4          | LCD instruction register (LOW)/data register (HIGH) select.    |

| mLCD_RW_WR <sup>[4]</sup>            | N9                                              | SUP8                    | DO                   | 0                                 | DIO4          | LCD 6800 read/write select or 8080 write enable (active HIGH). |

| mLCD_DB_0[4]                         | N8                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 0.                                                    |

| mLCD_DB_14                           | P9                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 1.                                                    |

| mLCD_DB_2[4]                         | N6                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 2.                                                    |

| mLCD_DB_3[4]                         | P6                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 3.                                                    |

| mLCD_DB_4[4]                         | N7                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 4.                                                    |

| mLCD_DB_5[4]                         | P7                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 5.                                                    |

| mLCD_DB_6[4]                         | K6                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 6.                                                    |

| mLCD_DB_7 <sup>[4]</sup>             | P5                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 7.                                                    |

| mLCD_DB_8[4]                         | N5                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 8/8-bit data 0.                                       |

| mLCD_DB_9[4]                         | L5                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 9/8-bit data 1.                                       |

| mLCD_DB_10[4]                        | K7                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 10/8-bit data 2.                                      |

| mLCD_DB_11[4]                        | N4                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 11/8-bit data 3.                                      |

| mLCD_DB_12[4]                        | K5                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 12/8-bit data 4/4-bit data 0.                         |

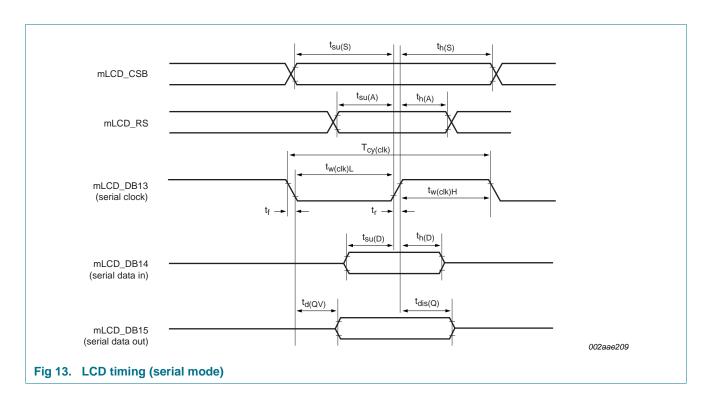

| mLCD_DB_13[4]                        | P4                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 13/8-bit data 5/4-bit data 1/serial clock output.     |

| mLCD_DB_14[4]                        | P3                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 14/8-bit data 6/4-bit data 2/serial data input.       |

| mLCD_DB_15 <sup>[4]</sup>            | N3                                              | SUP8                    | DIO                  | 0                                 | DIO4          | LCD data 15/8-bit data 7/4-bit data 3/serial data output.      |

| I <sup>2</sup> S/digital audio input |                                                 |                         |                      |                                   |               |                                                                |

| I2SRX_DATA0[4]                       | M10                                             | SUP3                    | DI/GPIO              | I                                 | DIO1          | I <sup>2</sup> S serial data receive input.                    |

| I2SRX_DATA1[4]                       | G14                                             | SUP3                    | DI/GPIO              | I                                 | DIO1          | I <sup>2</sup> S serial data receive input.                    |

| I2SRX_BCK0[4]                        | N10                                             | SUP3                    | DIO/GPIO             | I                                 | DIO1          | I <sup>2</sup> S bit clock.                                    |

| I2SRX_BCK1[4]                        | F14                                             | SUP3                    | DIO/GPIO             | I                                 | DIO1          | I <sup>2</sup> S bit clock.                                    |

| I2SRX_WS0[4]                         | P11                                             | SUP3                    | DIO/GPIO             | I                                 | DIO1          | I <sup>2</sup> S word select.                                  |

| I2SRX_WS1[4]                         | F13                                             | SUP3                    | DIO/GPIO             | I                                 | DIO1          | I <sup>2</sup> S word select.                                  |

**Table 4. Pin description** ...continued

Pin names with prefix m are multiplexed pins. See <u>Table 10</u> for pin function selection of multiplexed pins.

| Pin name                              | BGA<br>Ball | Digital<br>I/O<br>level | Application function | Pin<br>state<br>after<br>reset <sup>[2]</sup> | Cell type [3] | Description                                   |  |  |  |

|---------------------------------------|-------------|-------------------------|----------------------|-----------------------------------------------|---------------|-----------------------------------------------|--|--|--|

| I <sup>2</sup> S/digital audio output |             |                         |                      |                                               |               |                                               |  |  |  |

| mI2STX_DATA0[4]                       | M13         | SUP3                    | DO/GPIO              | 0                                             | DIO1          | I <sup>2</sup> S serial data transmit output. |  |  |  |

| mI2STX_BCK0[4]                        | M12         | SUP3                    | DO/GPIO              | 0                                             | DIO1          | I <sup>2</sup> S bit clock.                   |  |  |  |

| mI2STX_WS0[4]                         | M11         | SUP3                    | DO/GPIO              | 0                                             | DIO1          | I <sup>2</sup> S word select.                 |  |  |  |

| mI2STX_CLK0[4]                        | N14         | SUP3                    | DO/GPIO              | 0                                             | DIO1          | I <sup>2</sup> S serial clock.                |  |  |  |

| I2STX_DATA1[4]                        | F12         | SUP3                    | DO/GPIO              | 0                                             | DIO1          | I <sup>2</sup> S serial data transmit output. |  |  |  |

| I2STX_BCK14                           | E14         | SUP3                    | DO/GPIO              | 0                                             | DIO1          | I <sup>2</sup> S bit clock.                   |  |  |  |

| I2STX_WS14                            | G10         | SUP3                    | DO/GPIO              | 0                                             | DIO1          | I <sup>2</sup> S word select.                 |  |  |  |

| General Purpose IO (GPIO)             |             |                         |                      |                                               |               |                                               |  |  |  |

| GPIO0 <sup>17</sup>                   | K10         | SUP3                    | GPIO                 | I:PD                                          | DIO1          | General Purpose IO pin 0 (mode pin 0).        |  |  |  |

| GPIO1 <sup>1</sup>                    | J10         | SUP3                    | GPIO                 | I:PD                                          | DIO1          | General Purpose IO pin 1 (mode pin 1).        |  |  |  |

| GPIO2 <sup>[7]</sup>                  | L14         | SUP3                    | GPIO                 | I                                             | DIO1          | General Purpose IO pin 2 (mode pin 2).        |  |  |  |

| GPIO3                                 | B11         | SUP3                    | GPIO                 | I                                             | DIO1          | General Purpose IO pin 3.                     |  |  |  |

| GPIO4                                 | C11         | SUP3                    | GPI                  | I                                             | DIO1          | General Purpose input pin 4.                  |  |  |  |

| mGPIO5[4]                             | B6          | SUP3                    | GPIO                 | I                                             | DIO4          | General Purpose IO pin 5.                     |  |  |  |

| mGPIO6[4]                             | A6          | SUP3                    | GPIO                 | I                                             | DIO4          | General Purpose IO pin 6.                     |  |  |  |

| mGPIO7[4]                             | A5          | SUP3                    | GPIO                 | I                                             | DIO4          | General Purpose IO pin 7.                     |  |  |  |

| mGPIO8[4]                             | B5          | SUP3                    | GPIO                 | I                                             | DIO4          | General Purpose IO pin 8.                     |  |  |  |

| mGPIO9[4]                             | C5          | SUP3                    | GPIO                 | I                                             | DIO4          | General Purpose IO pin 9.                     |  |  |  |

| mGPIO10 <sup>[4]</sup>                | A4          | SUP3                    | GPIO                 | I                                             | DIO4          | General Purpose IO pin 10.                    |  |  |  |

| GPIO11                                | H13         | SUP3                    | GPIO                 | I                                             | DIO1          | General Purpose IO pin 11.                    |  |  |  |

| GPIO12                                | H10         | SUP3                    | GPIO                 | I                                             | DIO1          | General Purpose IO pin 12.                    |  |  |  |

| GPIO13                                | J12         | SUP3                    | GPIO                 | I                                             | DIO1          | General Purpose IO pin 13.                    |  |  |  |

| GPIO14                                | J14         | SUP3                    | GPIO                 | I                                             | DIO1          | General Purpose IO pin 14.                    |  |  |  |

| GPIO15                                | J13         | SUP3                    | GPIO                 | I                                             | DIO1          | General Purpose IO pin 15.                    |  |  |  |

| GPIO16                                | J11         | SUP3                    | GPIO                 | I                                             | DIO1          | General Purpose IO pin 16.                    |  |  |  |

| GPIO17                                | K12         | SUP3                    | GPIO                 | I                                             | DIO1          | General Purpose IO pin 17.                    |  |  |  |

| GPIO18                                | K14         | SUP3                    | GPIO                 | I                                             | DIO1          | General Purpose IO pin 18.                    |  |  |  |

| GPIO19                                | H11         | SUP3                    | GPIO                 | I                                             | DIO1          | General Purpose IO pin 19.                    |  |  |  |

| GPIO20                                | K13         | SUP3                    | GPIO                 | I                                             | DIO1          | General Purpose IO pin 20.                    |  |  |  |

| External Bus Interface (              | (EBI)/N     | AND flas                | h controller         |                                               |               |                                               |  |  |  |

| EBI_A_0_ALE[4]                        | В3          | SUP4                    | DO                   | 0                                             | DIO4          | EBI address latch enable.                     |  |  |  |

| EBI_A_1_CLE[4]                        | A2          | SUP4                    | DO                   | 0                                             | DIO4          | EBI command latch enable.                     |  |  |  |

| EBI_D_0[4]                            | G2          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 0.                               |  |  |  |

| EBI_D_1[4]                            | F2          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 1.                               |  |  |  |

| EBI_D_2[4]                            | F1          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 2.                               |  |  |  |

| EBI_D_3[4]                            | E1          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 3.                               |  |  |  |

| EBI_D_4[4]                            | E2          | SUP4                    | DIO                  | 1                                             | DIO4          | EBI data I/O 4.                               |  |  |  |

**Table 4.** Pin description ...continued

Pin names with prefix m are multiplexed pins. See Table 10 for pin function selection of multiplexed pins.

| EBI_D_5td         D1         SUP4         DIO         I         DIO4         EBI data I/O 5.           EBI_D_6td         D2         SUP4         DIO         I         DIO4         EBI data I/O 6.           EBI_D_8td         C1         SUP4         DIO         I         DIO4         EBI data I/O 7.           EBI_D_8td         B1         SUP4         DIO         I         DIO4         EBI data I/O 8.           EBI_D_9td         A3         SUP4         DIO         I         DIO4         EBI data I/O 9.           EBI_D_10td         A1         SUP4         DIO         I         DIO4         EBI data I/O 10.           EBI_D_11td         C2         SUP4         DIO         I         DIO4         EBI data I/O 11.           EBI_D_12td         G3         SUP4         DIO         I         DIO4         EBI data I/O 13.           EBI_D_14td         E3         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_D_15td         F3         SUP4         DIO         I         DIO4         EBI data I/O 15.           EBI_NOM_0_NONE_1d         H1         SUP4         DO         O         DIO4         NAND read enable (active LOW).                                                                                                                                                                 | Pin name                      | BGA<br>Ball | Digital<br>I/O<br>level | Application function | Pin<br>state<br>after<br>reset <sup>[2]</sup> | Cell type [3] | Description                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------|-------------------------|----------------------|-----------------------------------------------|---------------|------------------------------------|

| EBI_D_7[4]         C1         SUP4         DIO         I         DIO4         EBI data I/O 7.           EBI_D_8[4]         B1         SUP4         DIO         I         DIO4         EBI data I/O 8.           EBI_D_9[4]         A3         SUP4         DIO         I         DIO4         EBI data I/O 9.           EBI_D_10[4]         A1         SUP4         DIO         I         DIO4         EBI data I/O 10.           EBI_D_11[4]         C2         SUP4         DIO         I         DIO4         EBI data I/O 11.           EBI_D_12[4]         G3         SUP4         DIO         I         DIO4         EBI data I/O 12.           EBI_D_13[4]         D3         SUP4         DIO         I         DIO4         EBI data I/O 13.           EBI_D_14[4]         E3         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_D_N=15[4]         F3         SUP4         DIO         I         DIO4         EBI data I/O 15.           EBI_DOM_0_NOE[4]         H1         SUP4         DO         O         DIO4         NAND reade enable (active LOW).           NAND_NCS_0[4]         J1         SUP4         DO         O         DIO4         NAND reade ena                                                                                                                                                  | EBI_D_5[4]                    | D1          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 5.                    |

| EBI_D_8id         B1         SUP4         DIO         I         DIO4         EBI data I/O 8.           EBI_D_9id         A3         SUP4         DIO         I         DIO4         EBI data I/O 9.           EBI_D_10id         A1         SUP4         DIO         I         DIO4         EBI data I/O 10.           EBI_D_11id         C2         SUP4         DIO         I         DIO4         EBI data I/O 12.           EBI_D_12id         G3         SUP4         DIO         I         DIO4         EBI data I/O 13.           EBI_D_13id         D3         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_D_15id         E3         SUP4         DIO         I         DIO4         EBI data I/O 15.           EBI_DQM_0_NOEid         H1         SUP4         DIO         I         DIO4         EBI data I/O 15.           EBI_NWEid         J2         SUP4         DO         O         DIO4         NAND read enable (active LOW).           NAND_NCS_0id         H1         SUP4         DO         O         DIO4         NAND chip enable 0.           NAND_NCS_1id         J3         SUP4         DO         O         DIO4         NAND chip enable 2. <td>EBI_D_6[4]</td> <td>D2</td> <td>SUP4</td> <td>DIO</td> <td>I</td> <td>DIO4</td> <td>EBI data I/O 6.</td>                                         | EBI_D_6[4]                    | D2          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 6.                    |

| EBI_D_9id         A3         SUP4         DIO         I         DIO4         EBI data I/O 9.           EBI_D_10id         A1         SUP4         DIO         I         DIO4         EBI data I/O 10.           EBI_D_11id         C2         SUP4         DIO         I         DIO4         EBI data I/O 11.           EBI_D_12id         G3         SUP4         DIO         I         DIO4         EBI data I/O 13.           EBI_D_14id         E3         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_D_14id         E3         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_D_15id         F3         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_DQM_0_NOEid         H1         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_NWEid         J2         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_DQM_0_NOEid         H1         SUP4         DIO         I         DIO4         NAND readed enable (active LOW).           EBI_NWEid         J2         SUP4         DO         O         DIO4         NAND readed enable (                                                                                                                                                  | EBI_D_7[4]                    | C1          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 7.                    |

| EBI_D_10id         A1         SUP4         DIO         I         DIO4         EBI data I/O 10.           EBI_D_11id         C2         SUP4         DIO         I         DIO4         EBI data I/O 11.           EBI_D_12id         G3         SUP4         DIO         I         DIO4         EBI data I/O 12.           EBI_D_13id         D3         SUP4         DIO         I         DIO4         EBI data I/O 13.           EBI_D_15id         E3         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_DQM_0_NOEid         H1         SUP4         DIO         I         DIO4         EBI data I/O 15.           EBI_NWEid         J2         SUP4         DIO         I         DIO4         NAND read enable (active LOW).           NAND_NCS_0id         H1         SUP4         DO         O         DIO4         NAND write enable (active LOW).           NAND_NCS_0id         J1         SUP4         DO         O         DIO4         NAND write enable (active LOW).           NAND_NCS_0id         J1         SUP4         DO         O         DIO4         NAND chip enable 0.           NAND_NCS_0id         K1         SUP4         DO         O         DIO4 <td>EBI_D_8[4]</td> <td>B1</td> <td>SUP4</td> <td>DIO</td> <td>I</td> <td>DIO4</td> <td>EBI data I/O 8.</td>                                | EBI_D_8[4]                    | B1          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 8.                    |

| EBI_D_11id         C2         SUP4         DIO         I         DIO4         EBI data I/O 11.           EBI_D_12id         G3         SUP4         DIO         I         DIO4         EBI data I/O 12.           EBI_D_13id         D3         SUP4         DIO         I         DIO4         EBI data I/O 13.           EBI_D_14id         E3         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_D_15id         F3         SUP4         DIO         I         DIO4         EBI data I/O 15.           EBI_DQM_0_NOEid         H1         SUP4         DO         O         DIO4         NAND read enable (active LOW).           NAND_NCS_0id         J2         SUP4         DO         O         DIO4         NAND write enable (active LOW).           NAND_NCS_0id         J3         SUP4         DO         O         DIO4         NAND chip enable 0.           NAND_NCS_1id         J3         SUP4         DO         O         DIO4         NAND chip enable 2.           NAND_NCS_2id         K1         SUP4         DO         O         DIO4         NAND chip enable 3.           mNAND_RYBN0id         E6         SUP4         DI         I         DIO4                                                                                                                                                    | EBI_D_9[4]                    | А3          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 9.                    |

| EBI_D_12II         G3         SUP4         DIO         I         DIO4         EBI data I/O 12.           EBI_D_13II         D3         SUP4         DIO         I         DIO4         EBI data I/O 13.           EBI_D_13II         E3         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_D_15II         F3         SUP4         DIO         I         DIO4         EBI data I/O 15.           EBI_DQM_0_NOEII         H1         SUP4         DIO         O         DIO4         NAND read enable (active LOW).           EBI_NWEII         J2         SUP4         DO         O         DIO4         NAND write enable (active LOW).           NAND_NCS_0III         J1         SUP4         DO         O         DIO4         NAND chip enable 0.           NAND_NCS_1III         J3         SUP4         DO         O         DIO4         NAND chip enable 1.           NAND_NCS_2III         K1         SUP4         DO         O         DIO4         NAND chip enable 2.           NAND_RCS_3III         K2         SUP4         DO         O         DIO4         NAND ready/busy 0.           mNAND_RYBNIIII         E7         SUP4         DI         I         DIO4                                                                                                                                              | EBI_D_10[4]                   | A1          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 10.                   |

| EBI_D_13I <sup>4</sup> D3         SUP4         DIO         I         DIO4         EBI data I/O 13.           EBI_D_14I <sup>4</sup> E3         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_D_15I <sup>4</sup> F3         SUP4         DIO         I         DIO4         EBI data I/O 15.           EBI_DQM_0_NOEI <sup>4</sup> H1         SUP4         DO         O         DIO4         NAND read enable (active LOW).           EBI_NWEI <sup>4</sup> J2         SUP4         DO         O         DIO4         NAND write enable (active LOW).           NAND_NCS_0I <sup>4</sup> J1         SUP4         DO         O         DIO4         NAND chip enable 0.           NAND_NCS_1I <sup>4</sup> J3         SUP4         DO         O         DIO4         NAND chip enable 1.           NAND_NCS_2I <sup>4</sup> K1         SUP4         DO         O         DIO4         NAND chip enable 2.           NAND_RYBN0I <sup>4</sup> E6         SUP4         DI         I         DIO4         NAND ready/busy 0.           mNAND_RYBN1I <sup>4</sup> E7         SUP4         DI         I         DIO4         NAND ready/busy 2.           mNAND_RYBN3I <sup>4</sup> B4         SUP4         DI         I                                                                                                                 | EBI_D_11[4]                   | C2          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 11.                   |

| EBI_D_14[4]         E3         SUP4         DIO         I         DIO4         EBI data I/O 14.           EBI_D_15[4]         F3         SUP4         DIO         I         DIO4         EBI data I/O 15.           EBI_DQM_0_NOE[4]         H1         SUP4         DO         O         DIO4         NAND read enable (active LOW).           EBI_NWE[4]         J2         SUP4         DO         O         DIO4         NAND write enable (active LOW).           NAND_NCS_0[4]         J1         SUP4         DO         O         DIO4         NAND chip enable 0.           NAND_NCS_1[4]         J3         SUP4         DO         O         DIO4         NAND chip enable 1.           NAND_NCS_2[4]         K1         SUP4         DO         O         DIO4         NAND chip enable 2.           NAND_NCS_3[4]         K2         SUP4         DO         O         DIO4         NAND chip enable 3.           mNAND_RYBN0[4]         E6         SUP4         DI         I         DIO4         NAND ready/busy 0.           mNAND_RYBN3[4]         E7         SUP4         DI         I         DIO4         NAND ready/busy 3.           EBI_NCAS_BLOUT_0[4]         G1         SUP4         DO         O                                                                                                                                        | EBI_D_12[4]                   | G3          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 12.                   |

| EBI_D_15[4]         F3         SUP4         DIO         I         DIO4         EBI data I/O 15.           EBI_DQM_0_NOE[4]         H1         SUP4         DO         O         DIO4         NAND read enable (active LOW).           EBI_NWE[4]         J2         SUP4         DO         O         DIO4         NAND write enable (active LOW).           NAND_NCS_0[4]         J1         SUP4         DO         O         DIO4         NAND chip enable 0.           NAND_NCS_1[4]         J3         SUP4         DO         O         DIO4         NAND chip enable 1.           NAND_NCS_2[4]         K1         SUP4         DO         O         DIO4         NAND chip enable 2.           NAND_NCS_3[4]         K2         SUP4         DO         O         DIO4         NAND chip enable 3.           mNAND_RYBN0[4]         E6         SUP4         DI         I         DIO4         NAND ready/busy 0.           mNAND_RYBN1[4]         E7         SUP4         DI         I         DIO4         NAND ready/busy 1.           mNAND_RYBN3[4]         B4         SUP4         DI         I         DIO4         NAND ready/busy 3.           EBI_NCAS_BLOUT_0[4]         B1         SUP4         DO         O <td>EBI_D_13[4]</td> <td>D3</td> <td>SUP4</td> <td>DIO</td> <td>I</td> <td>DIO4</td> <td>EBI data I/O 13.</td>                     | EBI_D_13[4]                   | D3          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 13.                   |

| EBI_DQM_0_NOEI4         H1         SUP4         DO         O         DIO4         NAND read enable (active LOW).           EBI_NWEI4         J2         SUP4         DO         O         DIO4         NAND write enable (active LOW).           NAND_NCS_0I4         J1         SUP4         DO         O         DIO4         NAND chip enable 0.           NAND_NCS_1I4         J3         SUP4         DO         O         DIO4         NAND chip enable 1.           NAND_NCS_2I4         K1         SUP4         DO         O         DIO4         NAND chip enable 2.           NAND_NCS_3I4         K2         SUP4         DO         O         DIO4         NAND chip enable 3.           mNAND_NCS_3I4         K2         SUP4         DI         I         DIO4         NAND ready/busy 0.           mNAND_RYBN0I4         E6         SUP4         DI         I         DIO4         NAND ready/busy 1.           mNAND_RYBN3I4         B4         SUP4         DI         I         DIO4         NAND ready/busy 3.           EBI_NCAS_BLOUT_0I4         B1         SUP4         DO         O         DIO4         EBI lower lane byte select (7:0).           EBI_NRAS_BLOUT_1I4         H2         SUP4         DO                                                                                                                                 | EBI_D_14[4]                   | E3          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 14.                   |

| EBI_NWE[4]         J2         SUP4         DO         O         DIO4         NAND write enable (active LOW).           NAND_NCS_0[4]         J1         SUP4         DO         O         DIO4         NAND chip enable 0.           NAND_NCS_1[4]         J3         SUP4         DO         O         DIO4         NAND chip enable 1.           NAND_NCS_2[4]         K1         SUP4         DO         O         DIO4         NAND chip enable 2.           NAND_NCS_3[4]         K2         SUP4         DO         O         DIO4         NAND chip enable 3.           mNAND_NCS_3[4]         K2         SUP4         DI         I         DIO4         NAND ready/busy 0.           mNAND_RYBN0[4]         E6         SUP4         DI         I         DIO4         NAND ready/busy 1.           mNAND_RYBN3[4]         B4         SUP4         DI         I         DIO4         NAND ready/busy 3.           EBI_NCAS_BLOUT_0[4]         G1         SUP4         DO         O         DIO4         EBI lower lane byte select (7:0).           EBI_NRAS_BLOUT_1[4]         H2         SUP4         DO         O         DIO4         EBI upper lane byte select (15:8).           Secure one-time programmable memory                                                                                                                                  | EBI_D_15[4]                   | F3          | SUP4                    | DIO                  | I                                             | DIO4          | EBI data I/O 15.                   |

| NAND_NCS_0[4]         J1         SUP4         DO         O         DIO4         NAND chip enable 0.           NAND_NCS_1[4]         J3         SUP4         DO         O         DIO4         NAND chip enable 1.           NAND_NCS_2[4]         K1         SUP4         DO         O         DIO4         NAND chip enable 2.           NAND_NCS_3[4]         K2         SUP4         DO         O         DIO4         NAND chip enable 3.           mNAND_RYBN0[4]         E6         SUP4         DI         I         DIO4         NAND ready/busy 0.           mNAND_RYBN1[4]         E7         SUP4         DI         I         DIO4         NAND ready/busy 1.           mNAND_RYBN3[4]         B4         SUP4         DI         I         DIO4         NAND ready/busy 2.           mNAND_RYBN3[4]         D4         SUP4         DI         I         DIO4         NAND ready/busy 3.           EBI_NCAS_BLOUT_0[4]         G1         SUP4         DO         O         DIO4         EBI lower lane byte select (7:0).           EBI_NRAS_BLOUT_1[4]         H2         SUP4         DO         O         DIO4         EBI upper lane byte select (15:8).           Secure one-time programmable memory <t< td=""><td>EBI_DQM_0_NOE[4]</td><td>H1</td><td>SUP4</td><td>DO</td><td>0</td><td>DIO4</td><td>NAND read enable (active LOW).</td></t<> | EBI_DQM_0_NOE[4]              | H1          | SUP4                    | DO                   | 0                                             | DIO4          | NAND read enable (active LOW).     |

| NAND_NCS_14         J3         SUP4         DO         O         DIO4         NAND chip enable 1.           NAND_NCS_244         K1         SUP4         DO         O         DIO4         NAND chip enable 2.           NAND_NCS_344         K2         SUP4         DO         O         DIO4         NAND chip enable 3.           mNAND_RYBN044         E6         SUP4         DI         I         DIO4         NAND ready/busy 0.           mNAND_RYBN144         E7         SUP4         DI         I         DIO4         NAND ready/busy 1.           mNAND_RYBN344         B4         SUP4         DI         I         DIO4         NAND ready/busy 3.           EBI_NCAS_BLOUT_044         G1         SUP4         DO         O         DIO4         EBI lower lane byte select (7:0).           EBI_NRAS_BLOUT_144         H2         SUP4         DO         O         DIO4         EBI upper lane byte select (15:8).           Secure one-time programmable memory           VPP66         A9; SUP1/ Supply C9         PS3         Supply for polyfuse programming.           Pulse Width Modulation (PWM)                                                                                                                                                                                                                                        | EBI_NWE[4]                    | J2          | SUP4                    | DO                   | 0                                             | DIO4          | NAND write enable (active LOW).    |

| NAND_NCS_2 <sup>[4]</sup> K1 SUP4 DO O DIO4 NAND chip enable 2.  NAND_NCS_3 <sup>[4]</sup> K2 SUP4 DO O DIO4 NAND chip enable 3.  mNAND_RYBNO <sup>[4]</sup> E6 SUP4 DI I DIO4 NAND ready/busy 0.  mNAND_RYBN1 <sup>[4]</sup> E7 SUP4 DI I DIO4 NAND ready/busy 1.  mNAND_RYBN2 <sup>[4]</sup> B4 SUP4 DI I DIO4 NAND ready/busy 2.  mNAND_RYBN3 <sup>[4]</sup> D4 SUP4 DI I DIO4 NAND ready/busy 3.  EBI_NCAS_BLOUT_0 <sup>[4]</sup> G1 SUP4 DO O DIO4 EBI lower lane byte select (7:0).  EBI_NRAS_BLOUT_1 <sup>[4]</sup> H2 SUP4 DO O DIO4 EBI upper lane byte select (15:8).  Secure one-time programmable memory  VPP <sup>[6]</sup> A9; SUP1/ Supply - PS3 Supply for polyfuse programming.  Pulse Width Modulation (PWM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NAND_NCS_0[4]                 | J1          | SUP4                    | DO                   | 0                                             | DIO4          | NAND chip enable 0.                |

| NAND_NCS_3[4] K2 SUP4 DO O DIO4 NAND chip enable 3.  mNAND_RYBN0[4] E6 SUP4 DI I DIO4 NAND ready/busy 0.  mNAND_RYBN1[4] E7 SUP4 DI I DIO4 NAND ready/busy 1.  mNAND_RYBN2[4] B4 SUP4 DI I DIO4 NAND ready/busy 2.  mNAND_RYBN3[4] D4 SUP4 DI I DIO4 NAND ready/busy 3.  EBI_NCAS_BLOUT_0[4] G1 SUP4 DO O DIO4 EBI lower lane byte select (7:0).  EBI_NRAS_BLOUT_1[4] H2 SUP4 DO O DIO4 EBI upper lane byte select (15:8).  Secure one-time programmable memory  VPP[6] A9; SUP1/ Supply - PS3 Supply for polyfuse programming.  Pulse Width Modulation (PWM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NAND_NCS_1 <sup>[4]</sup>     | J3          | SUP4                    | DO                   | 0                                             | DIO4          | NAND chip enable 1.                |

| mNAND_RYBN0[4] E6 SUP4 DI I DIO4 NAND ready/busy 0.  mNAND_RYBN1[4] E7 SUP4 DI I DIO4 NAND ready/busy 1.  mNAND_RYBN2[4] B4 SUP4 DI I DIO4 NAND ready/busy 2.  mNAND_RYBN3[4] D4 SUP4 DI I DIO4 NAND ready/busy 3.  EBI_NCAS_BLOUT_0[4] G1 SUP4 DO O DIO4 EBI lower lane byte select (7:0).  EBI_NRAS_BLOUT_1[4] H2 SUP4 DO O DIO4 EBI upper lane byte select (15:8).  Secure one-time programmable memory  VPP[6] A9; SUP1/ Supply - PS3 Supply for polyfuse programming.  Pulse Width Modulation (PWM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NAND_NCS_2[4]                 | K1          | SUP4                    | DO                   | 0                                             | DIO4          | NAND chip enable 2.                |

| mNAND_RYBN1 <sup>[4]</sup> E7 SUP4 DI I DIO4 NAND ready/busy 1.  mNAND_RYBN2 <sup>[4]</sup> B4 SUP4 DI I DIO4 NAND ready/busy 2.  mNAND_RYBN3 <sup>[4]</sup> D4 SUP4 DI I DIO4 NAND ready/busy 3.  EBI_NCAS_BLOUT_0 <sup>[4]</sup> G1 SUP4 DO O DIO4 EBI lower lane byte select (7:0).  EBI_NRAS_BLOUT_1 <sup>[4]</sup> H2 SUP4 DO O DIO4 EBI upper lane byte select (15:8).  Secure one-time programmable memory  VPP <sup>[6]</sup> A9; SUP1/ Supply - PS3 Supply for polyfuse programming.  Pulse Width Modulation (PWM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NAND_NCS_3[4]                 | K2          | SUP4                    | DO                   | 0                                             | DIO4          | NAND chip enable 3.                |

| mNAND_RYBN2[4] B4 SUP4 DI I DIO4 NAND ready/busy 2.  mNAND_RYBN3[4] D4 SUP4 DI I DIO4 NAND ready/busy 3.  EBI_NCAS_BLOUT_0[4] G1 SUP4 DO O DIO4 EBI lower lane byte select (7:0).  EBI_NRAS_BLOUT_1[4] H2 SUP4 DO O DIO4 EBI upper lane byte select (15:8).  Secure one-time programmable memory  VPP[6] A9; SUP1/ Supply - PS3 Supply for polyfuse programming.  Pulse Width Modulation (PWM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | mNAND_RYBN0[4]                | E6          | SUP4                    | DI                   | I                                             | DIO4          | NAND ready/busy 0.                 |